# Lecture Notes in Computer Science

1823

Edited by G. Goos, J. Hartmanis and J. van Leeuwen

# Springer Berlin

Berlin Heidelberg New York Barcelona Hong Kong London Milan Paris Singapore Tokyo Marian Bubak Hamideh Afsarmanesh Roy Williams Bob Hertzberger (Eds.)

# High Performance Computing and Networking

8th International Conference, HPCN Europe 2000 Amsterdam, The Netherlands, May 8-10, 2000 Proceedings

#### Series Editors

Gerhard Goos, Karlsruhe University, Germany Juris Hartmanis, Cornell University, NY, USA Jan van Leeuwen, Utrecht University, The Netherlands

Volume Editors

Marian Bubak University of Mining and Metallurgy (AGH) Institute of Computer Science and Academic Computer Center CYFRONET al. Mickiewicza 30, 30-059 Cracow, Poland

E mails but als@ssi ach ads al

E-mail: bubak@uci.agh.edu.pl

Hamideh Afsarmanesh Bob Hertzberger

Universiteit van Amsterdam

Faculteit der Natuurwetenschappen, Wiskunde en Informatica

1098 SJ Amsterdam, The Netherlands E-mail: {bob,hamideh}@science.uva.nl

Roy Williams California Institute of Technology Caltech 158-79 Pasadena, CA 91125, USA E-mail:roy@cacr.caltech.edu

Cataloging-in-Publication Data applied for

Die Deutsche Bibliothek - CIP-Einheitsaufnahme

High performance computing and networking: 8th international conference; proceedings / HPCN Europe 2000, Amsterdam, The Netherlands, May 8 - 10, 2000. Marian Bubak . . . (ed.). - Berlin; Heidelberg; New York; Barcelona; Hong Kong; London; Milan; Paris; Singapore; Tokyo: Springer, 2000 (Lecture notes in computer science; Vol. 1823) ISBN 3-540-67553-1

CR Subject Classification (1991): C.2.4, D.1-2, E.4, F.2, G.1-2, J.1-2, J.3, J.6

ISSN 0302-9743

ISBN 3-540-67553-1 Springer-Verlag Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer-Verlag. Violations are liable for prosecution under the German Copyright Law.

Springer-Verlag is a company in the BertelsmannSpringer publishing group. © Springer-Verlag Berlin Heidelberg 2000 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Christian Grosche, Hamburg Printed on acid-free paper SPIN 10721098 06/3142 5 4 3 2 1 0

### **Preface**

This volume contains the proceedings of the international HPCN Europe 2000 event which was held in the Science and Technology Centre Watergraafsmeer, Amsterdam, the Netherlands, May 8-10, 2000.

HPCN (*High Performance Computing and Networking*) Europe event was organized for the first time in 1993 in Amsterdam as the result of several initiatives in Europe, the United States of America, and Japan. Succeeding HPCN events were held in Munich (1994), Milan (1995), Brussels (1996), and Vienna (1997), returning to Amsterdam in 1998 to stay.

The HPCN event keeps growing and advancing every year, and this year the event consisted of the scientific conference, focused workshops, and several associated events. The plenary lectures were presented by six renowned speakers:

- Henk van der Vorst, University of Utrecht, The Netherlands: Giant Eigenproblems within Reach,

- Wolfgang Gentzsch, CTO, Gridware Inc., Germany: The Information Power Grid is Changing our World,

- Bernard Lecussan, SupAero and ONERA/CERT/DTIM, France: Irregular Application Computations on a Cluster of Workstations,

- Miguel Albrecht, European Southern Observatory, Garching, Germany: Technologies for Mining Terabytes of Data,

- Hans Meinhardt, Max-Planck-Institut, Germany: The Algorithmic Beauty of Sea Shells, and

- Ingo Augustin, CERN, Geneva, Switzerland: Towards Multi-petabyte Storage Facilities.

The conference consisted of parallel tracks presenting 52 selected papers, and one track presenting 25 posters. The areas covered in the conference include: Industrial and General End-User Applications of HPCN, Computational and Computer Sciences, and this year the scope of the conference was further expanded by an additional area to emphasize the information management aspects, and the importance of the web-based cooperative application infrastructures.

In the area of Web-Based Cooperative Applications presented papers addressed: virtual enterprises and laboratories, cooperation coordination, as well as advanced web-based tools for tele-working. The area of Industrial and End-User Applications of HPCN consisted of papers focused on parallelisation of industrial codes, data-mining, and network applications. The papers presented in the area of Computational Science were dedicated to problem solving environments, metacomputing issues, load balancing and partition techniques, and new parallel numerical algorithms. In the area of Computer Science Research in HPCN the

following subjects were presented: Java in HPC, cluster computing, monitoring and performance, as well as compilation and low-level algorithms.

The newly emerging domains and applications of HPCN were covered within five thematic workshops and three associated events. The Java in High Performance Computing workshop (chaired by Vladimir Getov) focused on the use of Java in simulations, distributed resource management, on-line processing, data-intensive applications, and other emerging research topics that combine distributed object technology with networking. The LAWRA workshop (chaired by Jerzy Waśniewski) is devoted to the new, recursive formulation of basic algorithms in numerical software packages. Recursion leads automatically to better utilization of memory, offers very concise program structures, and results in significant speedup on modern SMP processors. Several challenging requirements of the virtual laboratory environments such as the problem solving and computing issues, data mining, and the collaborative work in emerging scientific and engineering domains were addressed within the Virtual Laboratory workshop (chaired by Bob Hertzberger). The main goal of the Cluster Computing workshop (chaired by Mark Baker and Wolfgang Gentzsch) is to find out how clusters, built with commodity-off-the-shelf hardware components and free or commonly used software, may redefine the concept of high performance and availability computing. At the EuroStore workshop (chaired by Fabrizio Gagliardi) efficiency, reliability, and manageability of very large storage systems (Multi-PB) were discussed. These problems, being of great importance for industrial applications, have been observed in high energy physics.

The three associated events of the HPCN 2000 conference were: the MPR event – Massive Parallel Computing (organized by Job Kleuver), the NCF event – Dutch Super Computing (organized by Jaap Hollenberg), and the symposium on Modeling and Simulation of Morphogenesis and Pattern Formation in Biology (organized by Jaap Kaandorp). This symposium addresses the investigation of self-organization and emergent behavior in biological systems with particle-based techniques.

The conference proceedings reflect the state of the art in several main areas of research, within the wide spectrum of HPCN. It is worth mentioning that the deadline for contributed papers was January 18, 2000. All the accepted papers and posters, as well as a selection of some papers presented at the workshops, are included in the proceedings. We thank all contributors for their cooperation, and we are pleased to observe the high quality of the submitted contributions. The best conference papers will also be selected later for publication in a special issue of the North-Holland journal Future Generation Computer Systems.

The selection of papers for HPCN 2000 would not have been possible without the support and careful evaluation of all the submissions by the members of the HPCN 2000 program committee, and their associated reviewers. The organizing committee is grateful for all the invaluable suggestions and the cooperation that we received from the reviewers. Their help made it possible to get at least three referee reports for each paper.

We would like to express our high gratitude to the members of the local organizing committee and the conference secretariat. Our sincere thanks go to Lodewijk Bos and Rutger Hamelynck. We greatly appreciate all the personal efforts and dedication of Anne Frenkel for both creating the HPCN Europe web pages and helping with the organization of paper distribution and review results, and those of Berry van Halderen for both setting up the on-line paper submission software and preparing papers for the proceedings.

We would like to thank the computer support groups, the FdNWI faculty of the University of Amsterdam, headed by Gert Poletiek, for the electronic communication support, and SARA in Amsterdam, headed by Jaap Hollenberg, for the distribution of the program and participation calls for HPCN 2000.

The organizers acknowledge the support of the DUTCH HPCN foundation, and the help of the University of Amsterdam for making its facilities available for this event.

March 2000

Marian Bubak Hamideh Afsarmanesh Bob Hertzberger Roy Williams

# Organization

#### Event Chairman:

Bob Hertzberger, University of Amsterdam, NL

### Scientific Organization:

Marian Bubak, University of Mining and Metallurgy (AGH), PL

Conference Chair

Hamideh Afsarmanesh, University of Amsterdam, NL

Conference Co-chair

Roy Williams, California Institute of Technology, USA

Conference Co-chair

## Program Committee

Hamideh Afsarmanesh Wlodzimierz Funika

Dan Aharoni Cesar Garita

Dick van Albada Wolfgang Gentzsch Vassil Alexandrov Alexandros Gerbessiotis

Farhad Arbab Vladimir Getov Jan Astalos Luc Giraud

Amnon Barak Alexander Godlevsky Ammar Benabdelkader Forouzan Golshani

Siegfried Benkner Ted Goranson Marian Bubak Andrzei M. Goscinski

Luis M. Camarinha-Matos Ralf Gruber

Paolo Cremonesi Necip Hamali

Przemyslaw Czerwinski Alfons Hoekstra

Miroslav Dobrucky Vasyl Horodisky

Asuman Dogac Cengiz Icdem

Jack Dongarra Peter Kacsuk

Iain Duff Ersin C. Kaletas

Dick Epema Nikos Karacapilidis Murat Ezbiderli Erwin Laure

Martin Frey Heather Liddell

Bob Madahar

Tomàs Margalef

Vladimir Marik

Eduard Mehofer

Hans Moritsch

Zsolt Nemeth

Gustaf Neumann

Deniz Oguz

George A. Papadopoulos Norbert Podhorszki Kees van Reeuwijk Alexander Reinefeld

Dirk Roose Erich Schikuta Giuseppe Serazzi Viera Sipkova Henk J. Sips Krzysztof Sowa Yusuf Tambag Arif Tumer

Henk A. van der Vorst

Roland Wagner Willy Weisz Roy Williams Kam-Fai Wong Zahari Zlatev

## Workshop Chairs:

Mark Baker (Cluster Computing) Fabrizio Gagliardi (Eurostore)

Vladimir S. Getov (Java in High Performance Computing)

Bob Hertzberger (Virtual Laboratory)

Jerzy Waśniewski (LAWRA - Linear Algebra with Recursive Algorithms)

#### **Associated Event Chairs:**

Jaap Kaandorp (Modeling and Simulation of Morphogenesis and Pattern Formation in Biology)

Job Kleuver (MPR - Massive Parallel Computing)

Jaap Hollenberg (NCF - Dutch Super Computing)

# Local Organization:

Lodewijk Bos

Rutger Hamelynck, Conference Office, University of Amsterdam

Anne Frenkel, University of Amsterdam

Berry van Halderen, University of Amsterdam

Joost Bijlmer, University of Amsterdam

# **Table of Contents**

| I Computational Science Track                                                     |    |

|-----------------------------------------------------------------------------------|----|

| Session 1 - Problem Solving Environments                                          |    |

| A Problem Solving Environment Based on Commodity Software                         | 3  |

| DOVE: A Virtual Programming Environment for High Performance Parallel Computing   | 12 |

| Session 3 - Metacomputing                                                         |    |

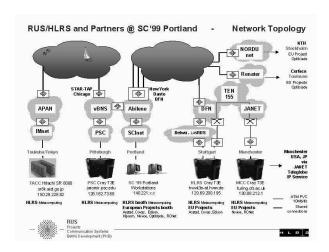

| The Problems and the Solutions of the Metacomputing Experiment in SC99            | 22 |

| Grid Computing on the Web Using the Globus Toolkit                                | 32 |

| Data Futures in DISCWorld                                                         | 41 |

| Session 6 - Partitioners / Load Balancing                                         |    |

| Algorithms for Generic Tools in Parallel Numerical Simulation                     | 51 |

| Dynamic Grid Adaption for Computational Magnetohydrodynamics                      | 61 |

| Parallelization of Irregular Problems Based on Hierarchical Domain Representation | 71 |

| Dynamic Iterative Method for Fast Network Partitioning                            | 81 |

| Session 9 - Numerical Parallel Algorithms                                         |    |

| ParIC: A Family of Parallel Incomplete Cholesky Preconditioners                   | 89 |

| A Parallel Block Preconditioner Accelerated by Coarse Grid Correction 99 C. Vuik, J. Frank                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------|

| Towards an Implementation of a Multilevel ILU Preconditioner on Shared-Memory Computers                                                        |

| Session 11 - Numerical Parallel Algorithms                                                                                                     |

| Application of the Jacobi–Davidson Method to Spectral Calculations in Magnetohydrodynamics                                                     |

| PLFG: A Highly Scalable Parallel Pseudo-random Number Generator for Monte Carlo Simulations                                                    |

| parSOM: Using Parallelism to Overcome Memory Latency in Self-Organizing Neural Networks                                                        |

| II Web-Based Cooperative Applications Track                                                                                                    |

| Web-Based Cooperative Applications Track                                                                                                       |

| Session 2 - Virtual Enterprises / Virtual Laboratories                                                                                         |

| <u> </u>                                                                                                                                       |

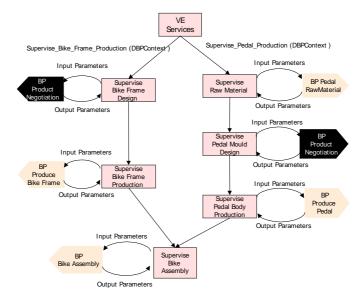

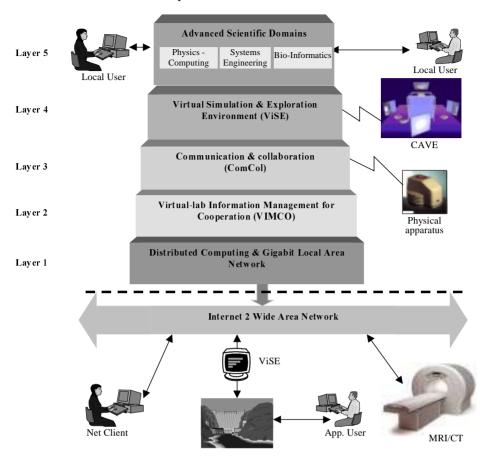

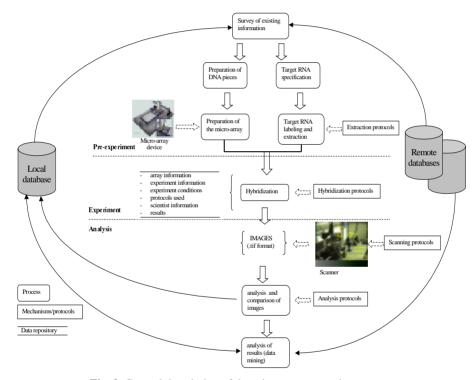

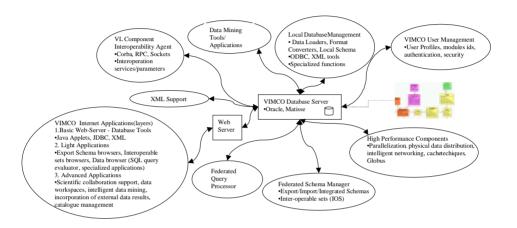

| Session 2 - Virtual Enterprises / Virtual Laboratories  Towards an Execution System for Distributed Business Processes in a Virtual Enterprise |

| Session 2 - Virtual Enterprises / Virtual Laboratories  Towards an Execution System for Distributed Business Processes in a Virtual Enterprise |

| Session 2 - Virtual Enterprises / Virtual Laboratories  Towards an Execution System for Distributed Business Processes in a Virtual Enterprise |

| Session 2 - Virtual Enterprises / Virtual Laboratories  Towards an Execution System for Distributed Business Processes in a Virtual Enterprise |

| Session 7 - Advanced Web-Based Tools for Tele-working                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------|

| Developing A Distributed Scalable Enterprise JavaBean Server                                                                |

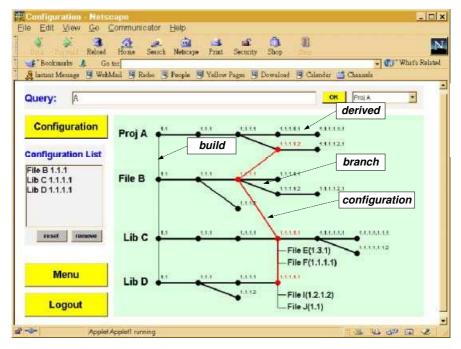

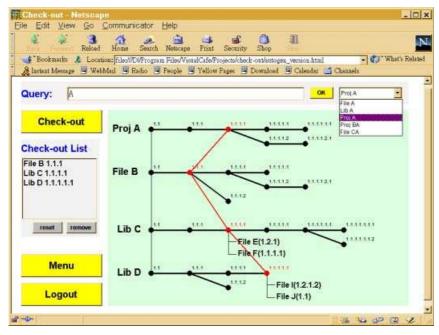

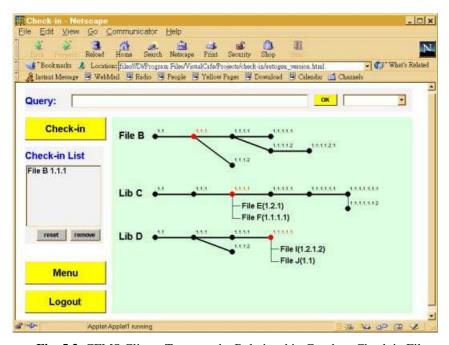

| CFMS - A Collaborative File Management System on WWW                                                                        |

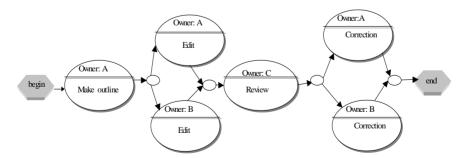

| Adding Flexibility in a Cooperative Workflow Execution Engine $\dots 227$ D. Grigori, H. Skaf-Molli, F. Charoy              |

| A Web-Based Distributed Programming Environment                                                                             |

| III Computer Science Track                                                                                                  |

| Session 5 - Monitoring and Performance                                                                                      |

| Performance Analysis of Parallel N-Body Codes                                                                               |

| Interoperability Support in Distributed On-Line Monitoring Systems 261<br>J. Trinitis, V. Sunderam, T. Ludwig, R. Wismüller |

| Using the SMiLE Monitoring Infrastructure to Detect and Lower the Inefficiency of Parallel Applications                     |

| Session 8 - Monitoring and Performance                                                                                      |

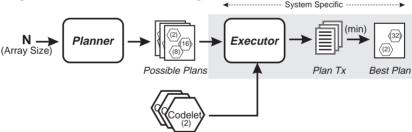

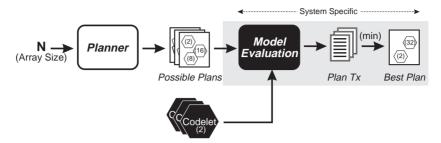

| Run-Time Optimization Using Dynamic Performance Prediction                                                                  |

| Skel-BSP: Performance Portability for Skeletal Programming                                                                  |

| Self-Tuning Parallelism                                                                                                     |

| A Novel Distributed Algorithm for High-Throughput and Scalable Gossiping                                                    |

| Session 13 - Low-Level Algorithms                                                                                           |

| Parallel Access to Persistent Multidimensional Arrays from HPF Applications Using Panda                                     |

| High Level Software Synthesis of Affine Iterative Algorithms onto Parallel Architectures                                 |

|--------------------------------------------------------------------------------------------------------------------------|

| Run-Time Support to Register Allocation for Loop Parallelization of Image Processing Programs                            |

| A Hardware Scheme for Data Prefetching                                                                                   |

| Session 15 - Java in HPC                                                                                                 |

| A Java-Based Parallel Programming Support Environment                                                                    |

| A Versatile Support for Binding Native Code to Java                                                                      |

| Task Farm Computations in Java                                                                                           |

| Session 16 - Clusters                                                                                                    |

| Simulating Job Scheduling for Clusters of Workstations                                                                   |

| A Compact, Thread-Safe Communication Library for Efficient Cluster Computing                                             |

| EPOS and Myrinet: Effective Communication Support for Parallel Applications Running on Clusters of Commodity Workstation |

| Distributed Parallel Query Processing on Networks of Workstations 427 $C.\ Soleimany,\ S.P.\ Dandamudi$                  |

| IV Industrial and End-User Applications Track                                                                            |

| Session 10 - Parallelisation of Industrial Applications                                                                  |

| High Scalability of Parallel PAM-CRASH with a New Contact Search Algorithm                                               |

| Large-Scale Parallel Wave Propagation Analysis by GeoFEM                                                                 |

| Explicit Schemes Applied to Aeroacoustic Simulations: The RADIOSS-CFD System                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Session 12 - Data Analysis and Presentation                                                                                                                                                       |

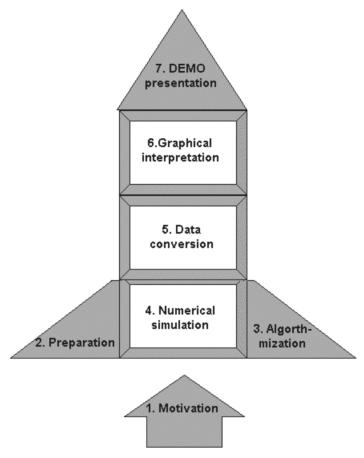

| Creating DEMO Presentations on the Base of Visualization Model 460 $E.V.\ Zudilova,\ D.P.\ Shamonin$                                                                                              |

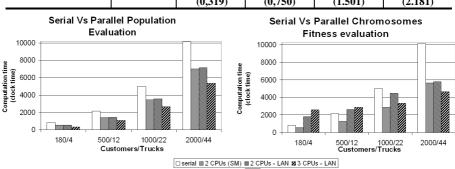

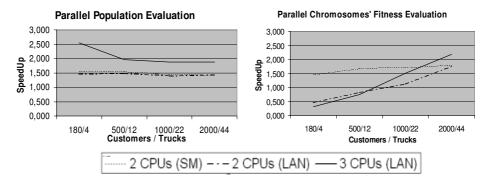

| Very Large Scale Vehicle Routing with Time Windows and Stochastic Demand Using Genetic Algorithms with Parallel Fitness Evaluation 467 M. Protonotarios, G. Mourkousis, I. Vyridis, T. Varvarigou |

| Extracting Business Benefit from Operational Data                                                                                                                                                 |

| Session 14 - Miscellaneous Applications                                                                                                                                                           |

| Considerations for Scalable CAE on the SGI ccNUMA Architecture 487 S. Posey, C. Liao, M. Kremenetsky                                                                                              |

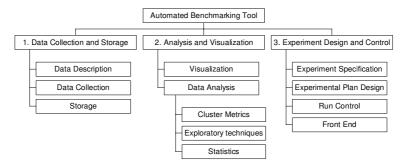

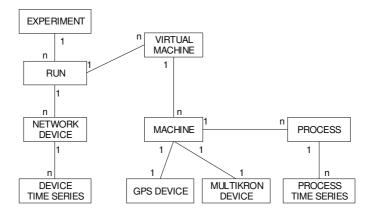

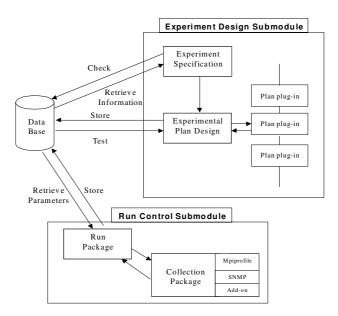

| An Automated Benchmarking Toolset                                                                                                                                                                 |

| Evaluation of an RCube-Based Switch Using a Real World Application 507 E.C. Kaletas, A.W. van Halderen, F. van der Linden, H. Afsarmanesh, L.O. Hertzberger                                       |

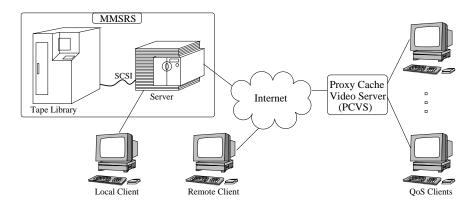

| MMSRS - Multimedia Storage and Retrieval System for a Distributed Medical Information System                                                                                                      |

| V Posters                                                                                                                                                                                         |

| Web-Based Cooperative Applications                                                                                                                                                                |

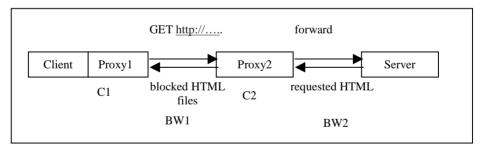

| Dynamically Transcoding Data Quality for Faster Web Access                                                                                                                                        |

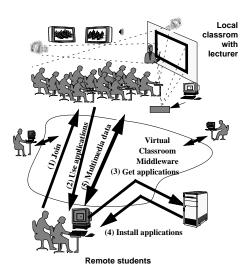

| Easy Teach & Learn <sup>(R)</sup> : A Web-Based Adaptive Middleware for Creating Virtual Classrooms                                                                                               |

| Industrial and End-User Applications                                                                                                                                                              |

| A Beowulf Cluster for Computational Chemistry                                                                                                                                                     |

| The APEmille Project                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A Distributed Medical Information System for Multimedia Data - The First Year's Experience of the PARMED Project                                                                                       |

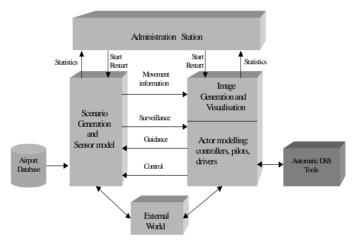

| Airport Management Database in a Simulation Environment                                                                                                                                                |

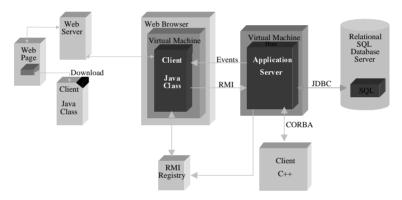

| Different Strategies to Develop Distributed Object Systems at University of La Laguna                                                                                                                  |

| DESIREE: DEcision Support System for Inuandation Risk Evaluation and Emergencies Management                                                                                                            |

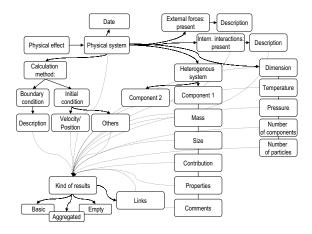

| Database System for Large-Scale Simulations with Particle Methods 558  D. Kruk, J. Kitowski                                                                                                            |

| Computational Science                                                                                                                                                                                  |

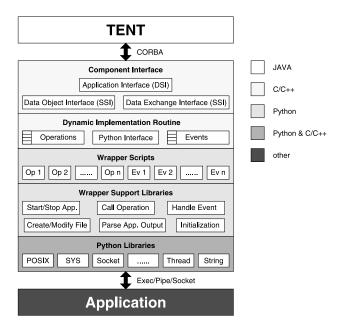

| Script Wrapper for Software Integration Systems                                                                                                                                                        |

| Implementation of Nested Grid Scheme for Global Magnetohydrodynamic Simulations of Astrophysical Rotating Plasmas                                                                                      |

| Parallel Multi-grid Algorithm with Virtual Boundary Forecast Domain Decomposition Method for Solving Non-linear Heat Transfer Equation 568 G. Qingping, Y. Paker, Z. Shesheng, D. Parkinson, W. Jialin |

| High Performance Computing on Boundary Element Simulations 572  J.M. Cela, A. Julià                                                                                                                    |

| Study of Parallelization of the Training for Automatic Speech Recognition 576 E.M. Daoudi, A. Meziane, Y.O. Mohamed El Hadj                                                                            |

| Parallelization of Image Compression on Distributed Memory Architecture 580 E.M. Daoudi, E.M. Jaâra, N. Cherif                                                                                         |

| Parallel DSMC on Shared and Hybrid Memory Multiprocessor Computers 584 G.O. Khanlarov, G.A. Lukianov, D.Yu. Malashonok, V.V Zakharov                                                                   |

| Population Growth in the Penna Model for Migrating Population                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------|

| Use of the Internet for Distributed Computing of Quantum Evolution 592 A.V. Bogdanov, A.S. Gevorkyan, A.G. Grigoryan, E.N. Stankova      |

| Computer Science                                                                                                                         |

| Debugging MPI Programs with Array Visualization                                                                                          |

| An Analytical Model for a Class of Architectures under Master-Slave Paradigm                                                             |

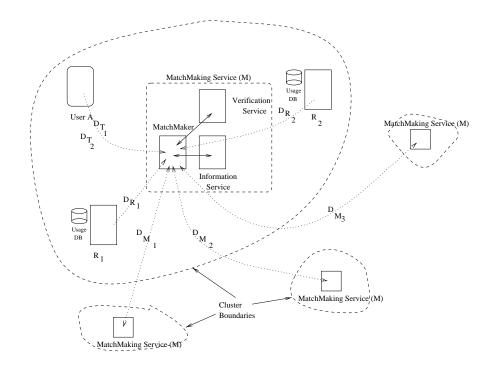

| Dynamic Resource Discovery through Match<br>Making 605 $\emph{O.F. Rana}$                                                                |

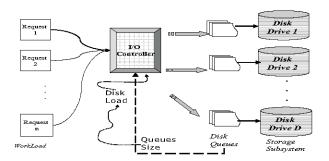

| A New Approach to the Design of High Performance Multiple Disk Subsystems: Dynamic Load Balancing Schemes                                |

| Embarrassingly Parallel Applications on a Java Cluster 614<br>B. $Vinter$                                                                |

| A Revised Implicit Locking Scheme in Object-Oriented Database Systems . 618 W. Jun, K. Kim                                               |

| Active Agents Programming in HARNESS                                                                                                     |

| VI Workshops                                                                                                                             |

| LAWRA Workshop                                                                                                                           |

| LAWRA Workshop: Linear Algebra with Recursive Algorithms:  http://lawra.uni-c.dk/lawra/                                                  |

| Java in HPC Workshop                                                                                                                     |

| Communicating Mobile Active Objects in Java                                                                                              |

| A Service-Based Agent Framework for Distributed Symbolic Computation 644 R.D. Schimkat, W. Blochinger, C. Sinz, M. Friedrich, W. Küchlin |

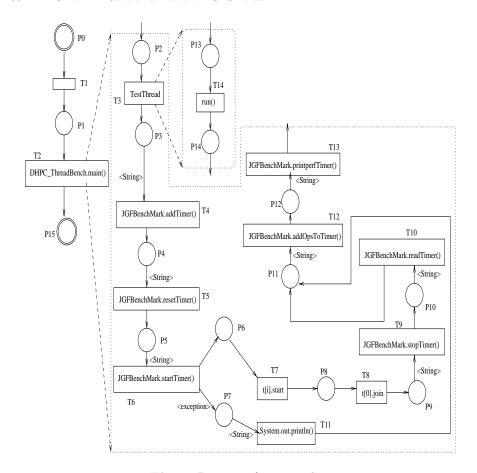

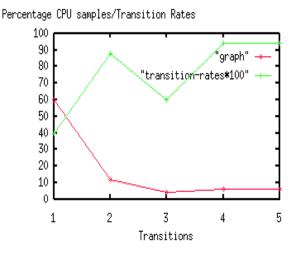

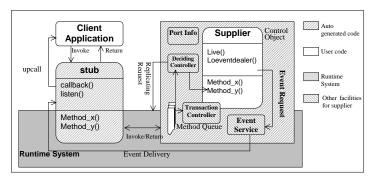

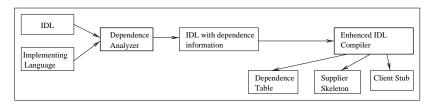

| Performance Analysis of Java Using Petri Nets                                                    |

|--------------------------------------------------------------------------------------------------|

| Cluster Computing Workshop                                                                       |

| A Framework for Exploiting Object Paralellism in Distributed Systems 668 $W.\ Chen,\ M.T.\ Yong$ |

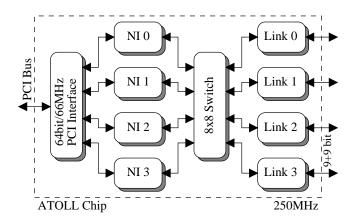

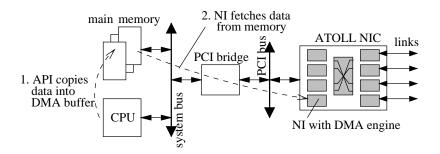

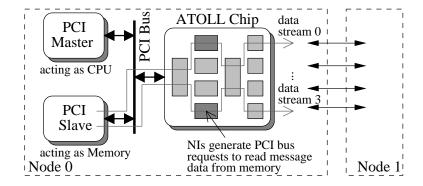

| Cluster SMP Nodes with the ATOLL Network: A Look into the Future of System Area Networks         |

| An Architecture for Using Multiple Communication Devices in a MPI Library                        |

| Results of the One-Year Cluster Pilot Project                                                    |

| Clusters and Grids for Distributed and Parallel Knowledge Discovery 708<br>$M.\ Cannataro$       |

| Author Index717                                                                                  |

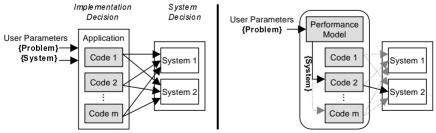

# A Problem Solving Environment Based on Commodity Software

David Lancaster and J.S. Reeve

Electronics & Computer Science University of Southampton, Southampton SO17 1BJ, U.K. djl@ecs.soton.ac.uk

Abstract. Following the common use of of commodity hardware to build clusters, we argue that commodity software should be harnessed in a similar way to support Scientific and Engineering work. Problem Solving Environments (PSE) provide the arena where commodity software technology can modernise the development and execution environment. We describe a PSE prototype based on the standard software infrastructure of Java Beans and CORBA that illustrates this idea and provides advanced PSE functionality at minimum effort for medium sized heterogeneus platforms.

#### 1 Introduction

In recent years, scientists and engineers in poorly funded University departments have realised that clusters of PC's provide a cost-effective computing platform for their computationally intensive needs. These clusters [1] are constructed from cheap, off-the-shelf, commodity hardware components and usually run free operating systems such as Linux.

The same forces that have led to the flood of cheap hardware components have also led to the availability of cheap commodity software. It is natural to propose that this software should also be harnessed towards the needs of academic scientists. G. Fox [2] has been a proponent of this idea and has identified the software supporting distributed information systems as being most relevant. In particular, the standardised software that supports web applications, such as CORBA[3], Java[4] and XML[5], is widely available, often freely or for nominal sums.

The proposed role for this commodity software is to modernise the software environment within which scientists and engineers develop and execute applications. The typical software environment for scientific work has changed little over many years, and often remains at the level of command line driven compilers and debuggers. To compile and execute code, the detailed idiosyncracies of each platform in a typically heterogeneus system must be recalled. Problem Solving Environments (PSE's) have been proposed [6] as a more modern environment. A PSE is a software environment that provides support for all stages in both the development and execution of problem solving code. Some PSE's provide further functionality but the essential ingredients are:

M. Bubak et al. (Eds.): HPCN 2000, LNCS 1823, pp. 3–11, 2000.

- Development: The PSE should follow modern software trends by being modular and allowing graphical programming. The components or modules perform well-defined computational functions relevant to the target field of the PSE: for example in engineering they may be solvers of various kinds or grid generators. The solution to a problem is achieved by composing diverse components into a full application that addresses the problem. Composition, which consists in wiring up the components may be done using graphical programming which is widely used in commercial fields and is generally held to improve programmer productivity. This approach enables novel ideas to be tested by rapidly prototyping complex combinations of components.

- Execution: A distributed hardware system is assumed, and the the PSE must be able to run each component (typically requiring substantial computation) on remote machines in a transparent manner. The hardware environment available to the users we have in mind is heterogeneous and there is considerable scope for improvements in efficiency by scheduling components to appropriately chosen machines. This is a time-consuming management task, and one gain from using a PSE will be that it avoids the need for the user to be concerned with details of the respective platforms. Infrastructure supporting seamless computing of this kind is provided by various projects such as Globus[7] and Unicore[8].

In this paper we show how a basic PSE with these features can rapidly and simply be put together using commodity software technologies: JavaBeans[4] and CORBA[3]. JavaBeans enable the PSE to use sophisticated graphical tools for development and CORBA addresses the requirements of transparently executing code on heterogeneous platforms.

As befits a prototype system we emphasise simplicity of design. The PSE is designed to use the commmodity layers in such a way as to minimize the additional infrastructure code that must be written and should be regarded as an experimental architecture. In this first step, we have tried to include all the basic functionality but we have not been deeply concerned about the performance. Even so we have incorporated some techniques, notably in data transfer and non-blocking CORBA calls, in order to hide latency.

In the remaining sections of this paper we give a more detailed description of the commodity software technologies, introduce the prototype PSE and explain the roles that the software layers play in this PSE. The next section describes the relevant features of JavaBeans and of CORBA before we proceed to a fuller description of the PSE prototype architecture in section 3. After a brief overview of related work, the conclusion summarises our experiences and mentions some of the directions for further research.

# 2 Commodity Software Technologies

The commodity technologies related to distributed computing that we have in mind include CORBA, Microsoft's DCOM, Java based software and proposals

put forward by the World Wide Web Consortium. It is not apparent which, if any, of these will survive in the future. Nonetheless they do have common characteristic features: they are cheap (often with free implementations), widely available and standardized. As a result of strong competition, implementations are robust and of high quality. These are the features needed in designing new software environments for Scientific/Engineering purposes. The resultant systems are intended to combine the necessary perfomance needed for computationally intensive applications with the rich functionality of commodity systems. In this paper we emphasise the functionality, but in the conclusion we will return to discuss the performance.

Our prototype PSE uses JavaBeans and CORBA. These are appropriate for a prototype that is intended to be used with a heterogeneous collection of medium sized machines such as PC clusters, small shared memory machines and individual workstations that run a variety of operating systems. A more highly featured PSE that was intended to be used with more substantial computing resources would also need software layers that connect to queuing systems and databases. To better organize the computational components and allow them to be easily shared, a large PSE might also benefit from software standards such as XML.

#### 2.1 JavaBeans

JavaBeans are reusable software components that can be manipulated visually in a Builder tool such as the Beanbox[9]. The beans are written in standard Java but conform to certain naming patterns that the builder tool uses to discover their properties.

Java beans fulfill the need for a sophisticated user interface that allows graphical programming by connecting computational components. In the prototype PSE, each bean represents a component that performs some computational function. The development stage of the PSE consists of selecting beans from a palette and wiring them together in a builder tool in such a way as to compose the computational components into an application that provides the means of solving the problem at hand. An approach of this sort should be familiar to anyone who has used tools such as AVS [10].

A fully functional PSE would have its own visual tool that provides all the builder functionality to wire up beans besides supporting the organisation of the palette of beans, various pieces of run-time support along with help and guidance tools. However, the aim of this work is to demonstrate how far one can proceed without such proprietary development, and although commercial builder tools may not provide all the functionality desired, they are interchangeable and support the majority of usage scenarios.

#### 2.2 CORBA

CORBA provides a framework for distributed computing. The features that endear it to industry are that it is object oriented, that it is inter-operable across

platforms and a variety of languages and that it is already a long-lived and well supported standard [3]. To enable the interoperability, interfaces are defined in a language known as IDL and communication takes place transparently through an ORB. There are many suppliers of ORB's [11] such as Sun who include an ORB in their JDK1.2.

CORBA provides a platform independent way of distributing the computations performed by the PSE so as to take advantage of high performance machines and software implementations. The components, or computational modules of the PSE are presented to the user in the form of the JavaBeans described above. These beans are only used to allow graphical composition, the actual computational code is not written in Java as part of the bean, but is in some other language (possibly legacy code) that resides on a different machine. The Java beans are hollow and merely make CORBA calls to the computational code.

For a small PSE with few components, it might be possible to decide in advance where each piece of computational code should run. Then, with the help of the CORBA nameservice the appropriate machine could be selected at runtime. In more sophisticated PSE's a scheduler would be used to select a machine to run the code depending on load and other factors.

## 3 Prototype

The discussion above should already have clarified the overall architecture of our prototype and the roles of the JavaBeans and CORBA. Before proceeding to describe the prototype in more detail, it may be worth being more explicit about one aspect of the overall architecture: the control flow. The whole PSE is based on a data flow model which is intuitive in this context and is made manifest in the way that the beans are wired together in the builder tool. Indeed, the information about the control flow has its origin in the act of wiring, and remains encapsulated in the builder tool. As soon as one component has completed its task and generated its data, control passes to the next bean which dispatches a request to the CORBA object that implements the computational work of the component. We emphasise this only to contrast it with the case where the control flow information in the builder tool is first abstracted and passed to a separate dispatcher (often combined with scheduler). Our choice of architecture is made for simplicity and to minimize the additional software that has to be written. It turns out that this architecture is extremely flexible and well adapted for computational steering.

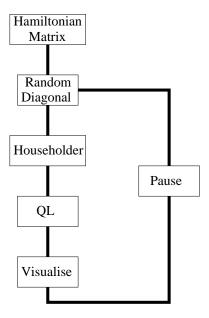

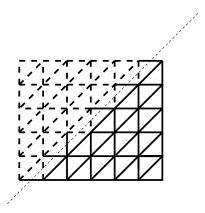

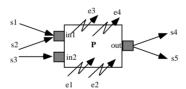

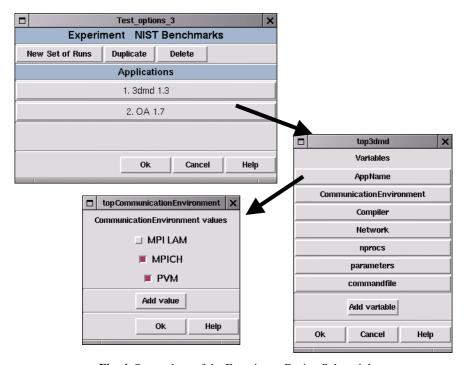

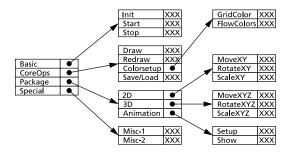

To illustrate the use of the PSE prototype and to make the following discussion more concrete we have implemented some simple components that perform operations to diagonalize a matrix. The method of diagonalization is standard and described in [12,13]. Below we list and briefly describe these components. Figure 1 shows how the components would typically be wired together in order to solve a certain problem in solid state physics. However, one of the main purposes of a PSE is that the components can be reused to solve other problems.

- Hamiltonian Matrix: Generate a matrix. The matrix corresponds to the Hamiltonian for a simple problem in solid state physics. It is symmetric and has zeros on the diagonal.

- Random Diagonal: Add random terms to the diagonal. This corresponds to a disordered medium in the solid state problem. The strength of the random terms is a variable parameter.

- Householder: Turn a symmetric matrix into tridiagonal form using a householder transformation.

- QL: Diagonalize a tridiagonal matrix using QL decomposition.

- **Visualize**: Display a matrix.

**Fig. 1.** Components wired in a Builder tool to diagonalize a matrix appearing in a problem of disordered media. The function of each component is described in the text. The direction of control flow is clockwise around the loop in this example.

The beans representing these components have interfaces described in the beaninfo class that prescribe how they can be wired together in the builder tool. Besides listing any parameters, this class lists the type and form of the inputs and outputs that the component expects. The JavaBean code is essentially limited to desribing these interfaces and the CORBA client code needed to call the computational module residing on a server. For this reason we call these beans "hollow". In order to avoid unnecessary data movement and thereby improve performance, the form of the inputs/outputs are not explicit matrices, but are CORBA references to data objects that contain the matrices.

The CORBA part of the prototype development requires an IDL for the system including the data objects for the matrices. This IDL is too long and detailed to include in a paper but is available on http://gather.ecs.soton.ac.uk/PSE/Docs. The CORBA servers have evolved since the beginning of this project and now provide facilities to manage the life-cycle of computational components.

We employ a performance enhancement that makes non-blocking CORBA calls to hide latency following a standard CORBA technique. Consider for example the Householder component which accepts a symmetric matrix and generates a tridiagonal matrix. When this bean starts to run, it first contacts the scheduler which provides an object reference on some remote machine to the computational class that implements the householder transformation. The bean then uses this reference to submit the object reference of the symmetric matrix data class and control then passes back to the bean which then waits. Meanwhile, the Householder object uses the matrix reference to transfer the matrix data to its local address space and then proceeds with the computation, finally creating a new matrix object in which to store the resulting tridiagonal matrix. The object reference to this tridiagonal matrix object is returned to the bean indicating completion of the job.

For the purposes of this work we implemented a scheduler that allows several versions of each component to exist on different machines and selects which one to use on request. This scheduler is dumb in the sense that the algorithm for selection is extremely simple, being either random or based on prior user choices. It does however provide the same kind of interface expected in a more sophisticated version. CORBA initialization employs a nameserver which is used to register servers that are started by hand on whatever remote machines are available. The scheduler contacts the nameserver to obtain all the information about which components are available on which machines.

The flow of control between one component and another takes place using the standard bean event mechanism and PropertyChangeEvents trigger this flow. For example, when the householder bean in the example above, obtains the reference to the tridiagonal matrix object, it fires a PropertyChangeEvent that is picked up by the next bean, in this case the QL bean, that has been wired to listen for such events.

As shown in the example in figure 1, there is no need to avoid loops when wiring the components. In this case there is no feedback of data up the loop, merely control flow. We have shown an explicit pause component that delays firing the PropertyChangeEvent and that allows the program to be controlled directly from the builder tool. In the situation shown in the figure, a Hamiltonian matrix of given size is generated once, and then on subsequent traversals of the loop different random terms are added to the diagonal and the resulting matrix is diagonalized. This corresponds to a typical need in the study of disordered systems where many realizations of the disorder must be averaged. A full implementation would contain components that perform the averaging automatically.

As befits a design based on CORBA, the prototype works on a wide variety of platforms, and we have used both workstations and PC's running various flavours of UNIX and Windows NT. We have used this project to test several ORBS with different functionality, including the JDK1.2 ORB, Orbacus[14] and JacORB[15]. Because we needed support for JDK1.2 at the start of this project, the user interface has been based on the beanbox builder tool. However, we expect that the components we have developed can be used in any commercial builder tool.

#### 4 Related Work

Although work on PSE's has been continuing for some years, before the recent flood of commodity software technology these efforts tended to use proprietary or specially developed infrastructure and have remained isolated.

The work closest to our own both in spirit and in use of commodity software is Webflow. The Webflow PSE [16] has a three tier architecture consisting of a Webflow editor front end, CORBA middle layer and Globus back end. The commodity middle layer has replaced an special purpose layer in a previous version of this tool. The main thrust of this work has been to allow meta-applications to be created simply at a high level. The connection to the Globus back end enables the PSE to target more substantial computational resources than our prototype. This work is now being used in a major PSE project called the Gateway [17].

Other PSE projects that use commodity software technology include JACO3 which couples simulations with CORBA and Java [18] and PSEware which provides a toolkit for building PSE's [19].

#### 5 Conclusion

We have demonstrated the ease with which commodity software technologies can be harnessed to provide advanced problem solving environments targeted for Scientists and Engineers. Our prototype is a proof-of-concept of this approach adapted for medium sized heterogeneous platforms.

As a first step, our demonstration has concentrated on providing the necessary functionality but the main challenge remains to obtain good performance out of systems built from commodity software. This challenge should not be confused with the difficulties in obtaining good performance from any PSE: in general there is a tradeoff between perfomance and flexibility and PSE's are certainly intended to be more flexible than the old-fashioned environment. The difficulty arises in deciding the level of granularity of the components: if the components are large, they will tend to be efficient but inflexible and *vice versa*. In the prototype we have described, CORBA is used to allow each computational component to be implemented in whatever language is appropriate (Fortran can be accommodated even though it has no CORBA binding [20]) and is thus expected to be efficient. The performance problems with commodity based PSE's

arise from communication between distributed objects. Work in this area, including high-performance CORBA implementations and comparisons between ORB's may be found in [21]. We have not provided any performance figures for the example included in the prototype because it was intended for illustrative purposes and is not an appropriate benchmark.

With the takeup of commodity software in this area, the range of possible PSE architecures is becoming more restricted so we may expect some convergence leading to the possibility of standardisation. Most useful would be standardisation of the form of the components, and work in this area is already in progress [22].

We also mention the improvements that would make this prototype PSE a more useful and robust tool. To allow the freer import and sharing of new components they should be described in some language such as XML along with tools that use this description to automatically create most of the bean and beaninfo code as well as providing a skeleton for the computational part of the code [23]. The other major area for improvement is in the scheduler, which should monitor load and provide a more sophisticated selection algorithm.

## Acknowledgments

David Lancaster would like to acknowledge discussions with Peter Lockey and Matthew Shields. This work was done in the context of a UK EPSRC grant entitled *Problem Solving Environments for Large Scale Simulations*.

#### References

- 1. D. Ridge, D. Becker, P. Merkey and T. Sterling. Beowulf: Harnessing the Power of Parallelism in a Pile-Of-PC's. Proc. 1997 IEE Aerospace Conference. See the Beowulf Project page at CESDIS:

- http://cesdis.gsfc.nasa.gov/linux/beowulf/beowulf.html

- G. Fox, W. Furmanski, T. Haupt, E. Akarsu and H. Ozdemir. HPcc as High Performance Commodity Computing on top of Integrated Java, CORBA, COM and Web Standards. Proc. of Europar 1998, Springer. 55-74, 1998.

- 3. The CORBA specification is controlled by the Object Management Group. http://www.omg.org/

- 4. Sun's central site for information about Java is at: http://java.sun.com/

- 5. World Wide Web Consortium, Extensible Markup Language (XML) http://www.w3.org/XML/

- E. Gallopoulos, E. Houstis and J.R. Rice. Problem Solving Environments for Computational Science. IEEE Comput. Sci. Eng., 1, 11-23, 1994.

- E. Gallopoulos, E. Houstis and J.R. Rice. Workshop on Problem Solving Environments: Findings and Recommendations. ACM Comp. Surv., 27, 277-279, 1995.

- I. Foster and C. Kesselman. Globus: A Metacomputing Infrastructure Toolkit. Int. J. Supercomp. Appl., 11, 115-128, 1997. http://www.globus.org

- 8. Uniform Access to Computing Resources. http://www.fz-juelich.de/unicore

- 9. The Beanbox is a free reference builder tool from Sun. Commercial tools are listed at: http://java.sun.com/beans/tools.html

- 10. AVS is produced by Advanced Visual Systems Inc. http://www.avs.com/

- 11. A list of ORB's is given at: http://adams.patriot.net/~valesky/freecorba.html/

- 12. W.H. Press, B.P.Flannery, S.A.Teukolsky and W.T.Vetterling. *Numerical Recipes*. In various languages. CUP.

- J. Reeve and M. Heath An Efficient Parallel Version of the Householder-QL Matrix Diagonalization Algorithm. Par. Comp. 25, 311-319, 1999.

- 14. http://www.ooc.com/ob.html

- 15. http://www.multimania.com/dogweb/

- T. Haupt, E. Akarsu and G. Fox. WebFlow: A Framework for Web Based Metacomputing. Proc. of HPCN 1999, Springer. 291-299, 1999.

- 17. http://www.osc.edu/~kenf/theGateway

- 18. http://www.arttic.com/projects/JACO3/default.html

- 19. http://www.extreme.indiana.edu/pseware/

- 20. Besides well known techniques of wrapping Fortran, some work on an F90 binding was done in the context of the Esprit PACHA project.

- 21. http://www.cs.wustl.edu/~schmidt/corba-research-performance.html

- 22. R. Armstron, D. Gannon, A. Geist, K. Keahey, S. Kohn, L. McInnes, S. Parker and B. Smolinski. *Toward a Common Component Architecture for High-Performance Scientific Computing*. Available from the CCA Forum: http://z.ca.sandia.gov/~cca-forum/

- 23. O.F. Rana, M. Li, D.W. Walker and M.Shields. An XML based Component Model for Generating Scientific Applications and Performing Large Scale Simulations in a Meta-Computing Environment. Available from: http://www.cs.cf.ac.uk/PSEweb/

# DOVE: A Virtual Programming Environment for High Performance Parallel Computing

Hyeong Do Kim, So-Hyun Ryu, and Chang Sung Jeong\*

Department of Electronics Engineering, Korea University, Anamdong 5-ka Sungbuk-ku, Seoul 136-701, Korea FAX: +82-2-926-7620, Tel: +82-2-3290-3229 kimhd@snoopy.korea.ac.kr csjeong@charlie.korea.ac.kr messias@snoopy.korea.ac.kr

Abstract. In this paper, we present a new parallel programming environment, which is called DOVE(Distributed Object-oriented Virtual computing Environment), based on distributed object model. A parallel program is built as a collection of concurrent and autonomous objects interacting with one another via method invocation. It appears to a user logically as a single virtual computer for a set of heterogeneous hosts connected by a network as if objects in remote site reside in one virtual computer. The main goal of DOVE is to provide users with easyto-use programming environment while supporting efficient parallelisms encapsulated and distributed among objects. Efficient parallelisms are supported by various types of method invocation and multiple method invocation to the object group. For the performance evaluation purpose of DOVE, we have developed two parallel applications both on DOVE and PVM. Our experiment shows that DOVE has better performance than PVM and provides an efficient and easy-to-use parallel programming environment for a set of heterogeneous and clustered computers.

#### 1 Introduction

During the last decade, increases in computing power of individual machines and advances in high-speed computer networks make clustered computer more attractive and considerable trend in high performance computing paradigm[1]. Currently, various programming environments have been developed for clustered computing environments. Most of the parallel programming environments for clustered computing are based on distributed shared memory model and message passing model.

Recently, distributed object models such as OMG CORBA[2], JAVA/RMI[3] and DCOM[4] have been introduced to tackle the problems inherent in distributed computing on a heterogeneous environment. Distributed object model consists of objects which interact via method invocation, while message passing

<sup>\*</sup> This work has been supported by KISTEP and KOSEF under contract 99-NF-03-07-A-01 and 981-0926-141-2.

M. Bubak et al. (Eds.): HPCN 2000, LNCS 1823, pp. 12-21, 2000.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2000

model consists of processes which communicate with each other via message passing. Distributed object model has several benefits over message passing model. It provides an easy programming environment by supporting transparency of distributed objects, plug and play of software as well as the advantages of object oriented programming such as reusability, extensibility, and maintainability through abstraction, encapsulation and inheritance. However, it lacks some functionalities for parallel applications, since they are based on client-server model.

In this paper, we present a new parallel programming environment, which is called DOVE (Distributed Object-oriented Virtual computing Environment), for clustered computing based on a distributed object model. The main goal of DOVE is to provide users with easy-to-use programming environment while supporting efficient parallelisms encapsulated and distributed among objects. An easy-to-use and transparent parallel programming environment is provided by heterogeneity achieved through automatic data marshalling and unmarshalling, stub and skeleton objects generated automatically by DOVE IDL compiler, and object life management and naming service offered by object manager. Thus, in DOVE, the code of a parallel program has little difference with the sequential one. For the performance evaluation purpose of DOVE, we have developed two parallel programs with applications to ray-tracing and genetic simulated annealing respectively both on DOVE and PVM.

The outline of our paper is as follows: In section 2, we describe previous works which are related to our work. In section 3, we present the details of DOVE object model, and in section 4, describe object manager. In section 5 and 6, we present an architecture of DOVE run-time system and its implementation respectively. In section 7, we present a performance comparison with PVM for two applications. Finally, a conclusion will be given in section 8.

#### 2 Related Work

In this section, we describe several parallel programming environments for clustered computing which are related to our work. MPI[5] is a single standard programming interface mainly designed for developing high performance parallel applications with emphasis on a variety of communication patterns and communication topology. However, MPI lacks in functionalities such as process control, resource management and fault-tolerance. PVM[6] is one of the most widely used distributed and parallel computing systems based on the message passing model, and connects together separate physical machines into a virtual computer by providing process control, simple message passing and packing constructs and dynamic process group management. In PVM, a daemon process, which runs on each host of a virtual machine, is used not only as process controller but also message router, which may result in communication bottleneck as all tasks heavily depend on daemon processes.

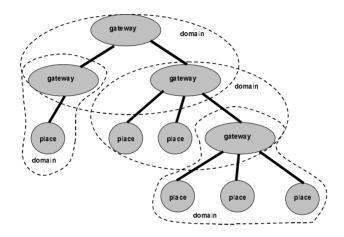

Legion[7] is an architecture based on a distributed object model, and designed to build system service which provides a virtual machine using shared object, shared name space, fault-tolerance. Legion uses data flow model as par-

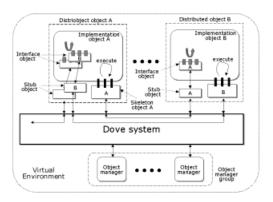

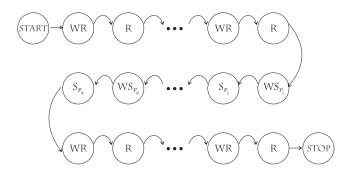

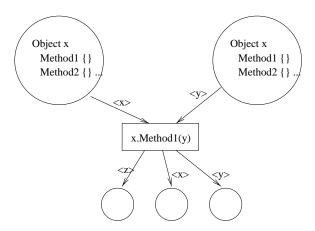

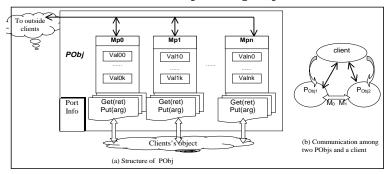

Fig. 1. DOVE Object Model.

allel computation model, and parallelisms are implicitly supported by the underlying runtime system. However, management of data dependency graph for every invocation as well as scheduling nodes of the graph may incur additional computation overhead, and no support for object group may cause communication inefficiency. CORBA[2] is a vendor-independent standard which aims at interoperability and portability of distributed applications. CORBA defines a distributed object model for accessing distributed objects. It includes an Interface Description Language, and a specification for the functionality of run-time systems that enable access to objects. But CORBA is based on client-server model rather than a parallel computing model, and hence it is not adequate to provide a parallel programming environment. It does not support group operations, and has some difficulties in implementing efficient parallelisms by using asynchronous communications.

# 3 DOVE Object Model

DOVE is based on distributed object model which consists of several distributed objects interacting with each other using method invocation mechanism. Distributed object is divided into interface object and implementation object. (See figure 1.) The interface object is distributed to applications which are to use the distributed object, and it provides interaction point to its corresponding implementation object. Users can issue a method invocation to the distributed object by invoking the method of its interface object, a local representative of the distributed object. Method invocation to the interface object is converted to the invocation message by stub object, and sent to the corresponding implementation object by DOVE run-time system. On the opposite side, the receiver's run-time system unmarshals the invocation message, and invokes the appropriate method of the target implementation object through skeleton object. A reply message is sent from the implementation object back to the interface object, and returned like a normal function call. This mechanism, which is called remote method invocation(RMI), allows transparent access to the object irrespective of whether

it resides in local or remote site. In DOVE, distributed object behaves either as client or server to interact with other distributed objects. In other words, it executes the implementation object for incoming RMI requests, while during the execution of the implementation object, it generates a remote invocation to the other distributed object using the interface object as a client. In DOVE, object manager exists per host and it provides a set of indispensable services, such as object creation, deletion and naming services, to build a transparent and easy-to-use clustered computing environment. A set of object managers constitutes a single object group which determines the domain of the virtual parallel environment that might encompass a huge number of machines and networks.

#### 3.1 Remote Method Invocation

DOVE provides three kinds of RMI to support various synchronization modes during data exchange between remote objects: synchronous, deferred synchronous and asynchronous RMIs. In synchronous RMI, sender is blocked until the corresponding reply is arrived. In deferred synchronous call, the sender can do other work immediately without awaiting the reply of the RMI, but later at some point must wait for the reply in order to use the return values. In asynchronous RMI, the sender can proceed without awaiting the reply similarly as in deferred synchronous one, but the corresponding upcall method is invoked on the arrival of its reply. These communication types are not the new ones, and often used to acquire high performance in distributed system.

In DOVE, these types of RMI are provided with more ease and intuitive way. Synchronous RMI has no constraint on its return type, and is identical to the general method invocation to local object. With deferred synchronous and asynchronous call, their return type is void. A value of type Waiter is returned for both of them, and used for synchronization between two threads one of which issues the RMI, and the other returns its reply respectively. In deferred synchronous RMI, sender uses the value of type Waiter to wait for the arrival of the corresponding reply. In asynchronous mode, an upcall method, specified when a RMI is issued, is invoked using a new thread generated automatically on the arrival of its reply. In this case, the value of type Waiter is used for waiting for the end of upcall method, not for the arrival of the reply.

#### 3.2 Object Group

In distributed system, group communication pattern is often used, since it provides simple and powerful abstraction. In DOVE, group communication mechanism is supported by introducing a new construct, object group, as means of grouping objects and naming them as one unit for RMIs. An interface object can be bound to its corresponding object group, and a RMI issued on the interface object is transparently multicast to each implementation object in the group. Interface object to the object group has the same interfaces as the one to the single object, and provides an interaction point with multiple objects in the object group so that user treats it just like a single object. Therefore, the

concept of object group allows users to do more simple programming, and to have chance to get better performance if the underlying communication layer supports multicasting facilities.

An object group can be created at any time by creating its interface object with GROUP flag. It is identified by its user-defined name and class name of the interface object. It is implicitly deleted according to their life time policy which is specified when the group is created. Distributed objects may join or leave their groups at any time by issuing join() or leave() methods on the interface object that is bound to the group. Each object group may consist of objects with different type, but should have one common type from which they are inherited, and only the methods inherited from the common type can be invoked.

#### 3.3 Multiple Method Invocation

A remote method invocation issued to an object group, called multiple method invocation(MMI), is transparently multicast to each object in the object group. Since the MMI to the object group may return one reply message per each member object in the group, the user needs to decide what replies to select from them. In DOVE, three types of MMI are supported: multicast/select, multicast/gather and scatter/gather. Multicast/select invocation is returned with only one reply which is obtained by applying operations such as minimum, maximum, and sum to the replies of objects in the group. Multicast/select and multicast/gather invocations multicast the same request to each member in the object group, while scatter/gather invocation multicasts the different requests to each member by storing them in sequences. Each sequence is an array of variable size. Both of multicast/gather and scatter/gather MMIs are returned with sequences which store each reply from the members in the object group. These MMIs can be also invoked in synchronous, deferred synchronous and asynchronous modes.

# 4 DOVE Object Manager

In order to provide users with a consistent and uniform view of the distributed clustered system, we need to provide additional services which can supports distribution transparencies. For these purpose, we design a special distributed object which is called *object manager*. Object manager is responsible for object life control such as creation, location and deletion of objects on its local host, naming service for binding object name to its physical address and event propagation to other object managers.

#### 4.1 Object Life Management

Object is created as a process either by a user at console or by an object manager on its local machine. When an interface object is newly created, its local object manager creates its corresponding implementation object on a remote

site by cooperating with the other object manager at the remote site. After the implementation object is created, it is connected to the interface object.

An object is created with three different life time: transient, fixed and permanent. A distributed object with transient life time automatically deletes itself after its creator has been disconnected from it. This mechanism efficiently keeps the system resource from being wasted by unused objects without any additional overhead. An independent and long-term object such as an object manager can be created with fixed or permanent life time. The life time of the object group is similar to that of object. A transient group is deleted when it is empty.

#### 4.2 Name Service

An object may have a name given by user, i.e. an alias represented by userdefined string when it is created. It is much easier and more user friendly to use an alias for object instead of its physical address. A name of the implementation object may be specified at the creation of the interface object. Then, the interface object is connected to the implementation object with the name immediately if it already exists; otherwise, after the implementation object with the name is created by object manager. Internally, the object reference is obtained from the name service of object manager, and used to connect to the existing implementation object. Naming service makes remote objects appear to users as the ones in one virtual computer by encapsulating binding operations from users, and hence provides an easy-to-use programming environment. Each object has its local cache to store binding information about its currently accessing objects, and first consult its local cache for binding information. If it fails, it requests the binding information to its local object manager. If the object manager does not contain the binding information, it multicasts the requests for the binding information to the object manager group. This kind of hierarchical naming service where the binding information is distributed in the local cache, local object manager and remote object managers, makes DOVE scalable.

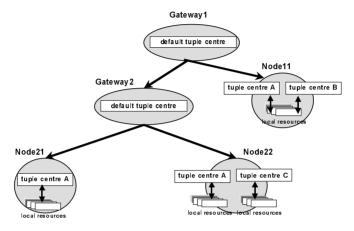

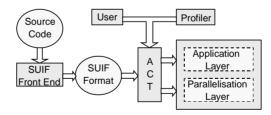

# 5 DOVE Run-Time System

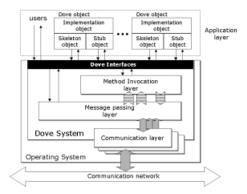

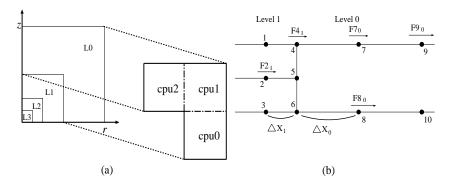

DOVE system is built as a multilayered architecture to provide the system modularity and extensibility as shown in figure 2. It fully supports various synchronization mechanisms and object group for RMI and MMI as well as heterogeneity through automatic marshalling and unmarshalling. The brief description of each layer is given below.

**Application Layer:** Application layer contains a user program which interacts with DOVE through stub and skeleton objects. Distributed objects are defined using *Interface Description Language(IDL)*. An IDL compiler is developed to automatically generate codes for stub and skeleton objects, which include codes for marshal and unmarshal methods. User can make use of different interfaces for the same operation to support diverse RMIs and MMIs. The calling semantics of method invocations are determined by their parameters. A method invoked

Fig. 2. Multi-layered Architecture of DOVE System.

through stub object is marshalled into an invocation structure which is then passed to method invocation layer.

Method Invocation Layer: Method invocation layer has a responsibility to provide the application layer with functionalities of the various types of RMIs in more ease and intuitive way. It marshals each invocation structure into an invocation message, and then passes it to a message passing layer after storing the calling semantic of the RMI into an invocation table to support various synchronization schemes. When the method invocation layer receives a reply message, it unmarshals the message and then performs proper actions such as signaling to the application layer or creating a new thread for execution of the upcall method, according to the semantic of the RMI.

Message Passing Layer: Message passing layer carries out object name binding to physical address, and delivers messages to distributed object using one of the underlying communication layers. Each communication layer can be implemented using any distributed protocol which makes use of different interfaces and naming schemes. The main purpose of message passing layer is to encapsulate method invocation layer from communication layer, and to provide the method invocation layer with uniform interfaces for message delivery and object group membership. Also, the message passing layer stores information about group membership, and takes care of MMI to the object group by using multicasting function if the communication layer supports it; otherwise by iterative execution of unicast function in the communication layer.

Communication Layer: In order to achieve the full functionality of DOVE system, the communication layer should be equipped with reliable unicast, reliable multicast and process group management. The minimal requirement for communication layer is reliable unicast likes TCP/IP. Currently, DOVE has installed two communication layers, one for reliable unicast using TCP/IP and another for reliable and ordered group communication using IP multicast.

## 6 DOVE Implementation

DOVE is implemented in C++ class library with a set of interfaces which are independent on the underlying platform including operating system and communication system. Each layer of DOVE system is implemented as an independent class with its own thread of control, and interacts with other layers through uniform and invariable interfaces in the library. An IDL compiler is also designed and implemented so that by compiling IDL, stub and skeleton objects are automatically generated in C++ codes using the DOVE class library. Currently, DOVE system is installed and tested on Microsoft's Windows NT/98 platform, and various types of Unix machine including Solaris, Irix and Linux.

#### 7 Evaluation

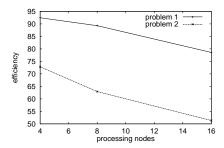

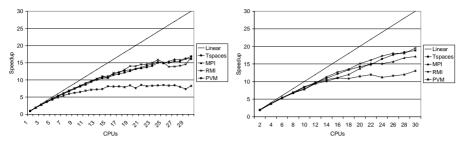

For the performance evaluation purpose of DOVE, we have developed two parallel applications: ray-tracing and genetic simulated annealing. They are implemented both on DOVE and PVM, and the experimental environment consists of 17 heterogeneous machines, two Ultrasparc1, two SGI O2, a SGI Octane, 9 Pentium II PCs running Linux and three Pentium II PCs running Windows NT/98 connected by 100Mbps ethernet. Since each machine has different computing powers, we have measured the relative performance with respect to Linux machine by comparing the execution time of the identical sequential program on each machine. Then, the expected speed up is computed as a sum of each relative performance of the participating machines. The efficiency of the parallel program is defined as the ratio of the actual speed up to the expected speed up.

#### 7.1 Parallel Ray-Tracing

Ray tracing [8] is a simple and powerful technique for rendering realistic images by tracing all the rays from eye through each pixel in the view plane. Since it requires high computation time for the calculation of intersections between rays and objects as well as the tracing of all the reflected and refracted rays, it has been considered as an adequate application for parallel computation. A parallel ray-tracing software is designed in master/slave scheme where one master task manager object interacts with ray tracer objects. Master/slave paradigm suits well in the clustered computing environment, since its dynamic nature of job scheduling can reduce the unbalance of computational power among the heterogeneous machines. Further, the task parallelism in master/slave scheme is very similar to the object parallelism in DOVE. One master task manager object is running on a Ultrasparc1 workstation for job distribution, and each of ray tracer objects on the other machine. Task manager object schedules the assignment of pixels to ray tracer objects which in turn calculate the value of each pixel. The relative performance of the machines obtained by executing the identical sequential ray-tracing program is shown in table 1. Table 2 shows the execution time, speed up and efficiency of ray-tracing according to the number

| machines      | $M_1$     | $M_2$     | $M_3$     | $M_4$     | $M_5$      | $M_6$   | $M_7$    |

|---------------|-----------|-----------|-----------|-----------|------------|---------|----------|

| OS            | Linux     | Win98     |           |           | Solaris2.5 |         |          |

| (spec.)       | (PII-300) | (PII-300) | (PII-366) | (PII-300) | (USparc1)  | $(O_2)$ | (Octane) |

| running time  | 427.475   | 312.460   | 253.670   | 307.602   | 858.340    | 781.636 | 466.224  |

| relative perf | 1.0       | 1.368     | 1.685     | 1.390     | 0.498      | 0.547   | 0.917    |

Table 1. Measurement of Relative Performance for Ray-Tracing.

**Table 2.** Performance Results of Parallel Ray-Tracing (Parenthesis in number of ray tracers represents a machine used for running an additional ray tracer object.)

| number           | r of ray tracers | $1(M_1)$ | $2(M_1)$ | $4(M_{3,5})$ | $8(M_{1,1,4,6})$ | $12(M_{1,2,6,7})$ | $16(M_{1,1,1,1})$ |

|------------------|------------------|----------|----------|--------------|------------------|-------------------|-------------------|

| expected speedup |                  | 1.0      | 2.0      | 4.183        | 8.120            | 11.952            | 15.952            |

|                  |                  | 427.475  | 217.300  | 104.298      |                  | 37.790            | 29.630            |

| DOVE             | speedup          | 1.0      | 1.967    | 4.099        | 7.781            | 11.312            | 14.931            |

|                  | efficiency(%)    | 100.0    | 98.36    | 97.98        | 95.83            | 94.64             | 93.6              |

|                  | time(sec)        | 427.475  | 227.622  | 107.803      |                  | 38.566            | 29.336            |

| PVM              | speedup          | 1.0      | 1.878    | 3.965        | 7.604            | 11.084            | 14.572            |

|                  | efficiency(%)    | 100.0    | 93.900   | 94.796       | 93.646           | 92.740            | 91.347            |

of ray tracers. As the number of ray tracer increases, DOVE shows an almost linear speedup and better performance than PVM. This results from the fact that in DOVE, computation and communication between objects can be efficiently overlapped using asynchronous RMI, and that DOVE executes RMIs directly to the object, while in PVM all messages from different processes are routed through daemon process which runs in each host, producing overhead in daemon process.

## 7.2 Parallel Genetic Simulated Annealing

GSA(Genetic Simulated Annealing)[9] is a hybrid method which exploits the genetic algorithm and the local selection strategy of simulated annealing. This approach eliminates the processing bottleneck of global selection by making the selection decisions locally.